جزوه های برای یادگیری FPGA و زبان VHDL

فایل PDF جزوه ی آموزشی FPGA و VHDL با Quartus

دانلود فایل ورد آموزش FPGA ,VHDL با QUARTUS

مشخص کردن پورتها در ISE برای پروگرام کردن FPGA

دانلود فیلم های آموزشی FPGA

| session | Description | Hi Res |

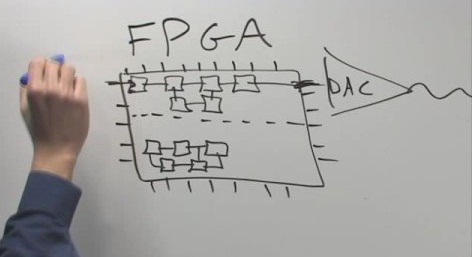

| 1 | What is an FPGA? What is the internal architecture of an FPGA? |

part1 part2 (save link as) |

| 2 | What is synthesis? What is a hardware description language? |

part1 part2 (save link as) |

| 3 | modules definition in verilog calling modules inside each other the meanin of top module |

part1 part2 (save link as) |

| 4 | Combinational circuit description in verilog using assign statement |

part1 part2 (save link as) |

| 5 | simulating a design using active hdl simulator how to generate a test bench to simulate a design |

SORRY! LOST! |

| 6 | describing sequential logic circuits using always statement |

DOWNLOAD (save link as) |

| 7 | describing logic circuits using assign and always statements |

DOWNLOAD (save link as) |

| 8 | Practical synthesis using Synplify - Design implementation using Xilinx ISE - Inspecting FPGA internal architecture using FPGA Editor - Pin assignment using Plan Ahead |

DOWNLOAD (save link as) |

| 9 | Numbers in verilog - Procedural continous Assignment - using always blocks to describe combination circuits - basic definition of tri-state buffers in verilog |

DOWNLOAD (save link as) |

| 10 | Input-output ports in verilog , desiging circuits with inout ports - two dimensional arrays in verilog - designing a simple SRAM module - using for loops in verilog |

DOWNLOAD (save link as) |

| 11 | Solving some sample verilog design problems, talking about verilog `define and verilog parameter statements |

DOWNLOAD (save link as) |

| 12 | parametric modules, basic architecture of FIFOs, verilog case statement |

DOWNLOAD (save link as) |

| 13 | Design simulation basics, the definition of design under test, tester and test bench. initial statement. indicating delay value in verilog code. timsescale statement. forever statement. begin-end and fork-join statements. blocking and none blocking assignments. | DOWNLOAD (save link as) |

| 14 | define statement. Sample verilog module design, test bench creation and simulation. Using modelsim for design simulation. Verilog system calls: fwrite, fread, random and ... | DOWNLOAD (save link as) |

| 15 | Sample top-down design containing multiple modules. design simulation using modelsim and synthesis using synplify synthesis tool. RTL synthesis and technology mapping steps. | DOWNLOAD (save link as) |

| 16 | Common mistakes in verilog coding. Introducing team design techniques. developing large modules with multiple developers. Introduction to cores and Xilinx core generator software. | DOWNLOAD (save link as) |

| 17 | More about cores. Where to use what family of FPGA for our project. Describing a simple state machine in verilog. solving homework problems in class. | DOWNLOAD (save link as) |

| 18 | Using Xilinx core generator to produce block memory cores, How to instantiate and use cores in Verilog, Simulating designs containing cores using ModelSim, Synthesizing designs containing cores | DOWNLOAD (save link as) |

| 19 | Using single port and dual port memories in designs, About FIFOs and width converter FIFOs, Post route simulation using ModelSim software, SDF file, Usign FPGA Editor, User constraints file and defining timing constraints | DOWNLOAD (save link as) |

| 20 | Clock network in FPGA, Digital clock manager and related components, Clock delay and clock skew, defining timing constraints, offset in, offset out and period definitions. | DOWNLOAD (save link as) |

| 21 | more on circuit timing and delay, using clock DLL for phase compensation of clock signal, | DOWNLOAD (save link as) |

| 22 | Retiming, more on usage of clock DLL, using DLL to generate external clock signals | DOWNLOAD |

| 22-2 | introduction to PicoBlaze | --- |

| 23 | Basics of PicoBlaze, PicoBlaze ports and signals, Important PicoBlaze instructions, Developing Verilog code to use PicoBlz, writing assembly code for PicoBlaze, Simulating FPGA designs based on PicoBlaze | DOWNLOAD (save link as) |

| 24 | Developing embedded systems for Xilinx FPGAs, Basic definitions about PowerPC and Microblaze CPUs, Basic structure of A PowerPC/Microblaze based embedded system, using Xilinx Embedded Development kit to develope basic FPGA based embedded systems. | DOWNLOAD (save link as) |

| 25 | Desiging a complete system for FPGA, Clock management, Designing and using FIFOs, Using HDL designer to design digital systems | DOWNLOAD (save link as) |

| 26 | More on desiging and using FIFOs, Using Timing designer to generate waveform prior to begining HDL coding | DOWNLOAD (save link as) |

| 27 | Using Finite State Machines for Digital HDL design, using HDL designer to create state machines, Showing the relation between your HDL code and circuit timings | DOWNLOAD (save link as) |

| 28 | Writing verilog code for FSM, talking about FIFO latency in read operation, countining the design of a complete system using HDL designer tool | DOWNLOAD (save link as) |

| 29 | Countinuing the design of the complete digital system | DOWNLOAD (save link as) |

جزوات آموزشی modelsim:

یکی از بهترین و حرفه ای ترین نرم افزارها برای طراحی و شبیه سازی برنامه های VHDL با قابلیت های بالا نرم افزار ModelSim10.0C می باشد .