این خودآموز به زبان فارسی نگاشته شده و برای آشنایی مقدماتی با نحو زبان Verilog و تواناییهای آن مفید است، مخاطب این خودآموز آن دسته از علاقهمندانی میباشند كه با زبان Verilog آشنایی ندارند.زبانهای توصیف سختافزار یكی از مهمترین ابزارهای مدرن طراحی سختافزارها میباشد كه كاربرد آنها در صنعت رو به افزایش است به طوری كه امروزه عضو جدا نشدنی فرایند طراحی تا پیاده سازی سختافزارهای مدرن به شمار میروند.

با توجه به اینكه زبانهای توصیف سختافزار یكی از مهمترین ابزارهای توسعه جنبش سختافزار آزاد به شمار میروند، در این مقاله به طور مفصل آنها را معرفی و مقایسه كردهایم، در پایان نیز تعدادی خودآموز و مرجع قابل دانلود جهت فراگیری این زبانها در اختیار بازدیدكنندگان قرار گرفته است.

فهرست بخش های مقاله :

- تكامل طراحی دیجیتال به كمك كامپیوتر

- زبان توصیف سختافزار چیست ؟

- زبان توصیف سختافزار VHDL

- زبان توصیف سختافزار Verilog

- Verilogدر برابر VHDL

- انتخاب یك زبان توصیف سختافزار

تكامل طراحی دیجیتال به كمك كامپیوتر :

طراحی مدارات دیجیتال از 25 سال گذشته تا كنون بسیار متحول گشته است، مدارهای دیجیتال ابتدایی كه به سختی میتوان نام سختافزار را بر روی آنها گذاشت، با لامپهای خلا و تعداد اندكی ترانزیستور ساخته میشدند.با ظهور تكنولوژی مدار مجتمع، امكان پیادهسازی مدارات دیجیتال بر روی یك تراشه فراهم گردید. اولین نسل مداراتمجتع یا IC ها، SSI سر نام Small Scale Integration نام دارد كه در این نسل تراشهها با تعداد بسیار اندكی ترانزیستور و گیتهای منطقی ساخته میشدند، پس از آن حجم مجتمع سازی در نسلهایMSI سر نام Medium Scale Integration و LSI سر نام Large Scale Integration به سرعت گسترش یافت و به طوری كه امكان مجتمع سازی هزاران گیت منطقی، در داخل یك تراشه برای طراحان سختافزار فراهم آمده بود. در این مرحله روند طراحی بسیار پیچیده و دشوار گردیده بود و طراحان نیاز داشتند تا بخشی از مراحل طراحی را به كامپیوتر بسپارند. به كمك ابزارهای طراحی دیجتال كامپیوتری یا CAD Toolها طراحان توانستند كامپیوتر را در فرایند طراحی اجزای خود سهیم سازند.

با پیشرفت نسل VLSI سر نام Very Large Scale Integration امكان طراحی مدارات مجتمع با میلیونها ترانزیستور فراهم گشته است(مانند تصویر بالا). به دلیل پیچیدگی بسیار زیاد این مدارات ،طراحی و ارزیابی عملكرد آنها به روشهای سنتی دیگر میسر نیست، به همین خاطر ایدهای جهت توصیف طرح به یك زبان قابل فهم برای كامپیوتر مطرح گردید تا زمینه حضور كامپیوتر در پروسه طراحی یك مدار VLSI گستردهتر گشته و مسائل طراحی و ارزیابی در پروسه طراحی یك سختافزار جدید، با الگوریتمهای از پیش تعریف شده، پردازش شوند.

زبان توصیف سختافزار چیست ؟

HDL سر نام Hardware Description Language ، به خانوادهای از زبانهای برنامهنویسی گفته میشود كه جهت مدلسازی عملكرد بخشی از یك سختافزار به كار گرفته میشوند. توصیف سختافزار به كمكHDLها به دو شكل كلی امكان پذیر است:

روش اول: مدلسازی ساختاری سختافزار، كه با تشرح ارتباطات خارجی، اجزای تشكیل دهنده داخلی و اتصالات میانها، جهت توصیف ساختار و اجزای تشكیل دهنده یك سختافزار به كار برده میشود.

روش دوم: مدلسازی رفتاری سختافزار، جهت توصیف انتزاعی رفتار یك سختافزار بدون در نظر گرفتن جزئیات ساختار آن میباشد كه بدون لحاظ كردن اجزای تشكیل دهنده، به توصیف خروجیهای مدل بر اساس تابعی از ورودیهای آن میپردازد. مدلسازی رفتاری یك سختافزار در سطوح مختلفی از انتزاع صورت میپذیرد كه سطوح بالاتر رفتار سختافزار را به صورت چكیدهتر با جزئیات كمتری نسبت به سطوح پایین تر انتزاع، توصیف میكنند.

طراحی یك سختافزار بر اساس طرح شماتیك مداری كه در گذشته از آن به وفور استفاده میشد، با اینكه شامل اطلاعات بسیار كاملی در مورد سختافزار و اجزای تشكیل دهنده آن بود، اما در توصیف طرحهای بزرگ به خاطر حجم بسیار زیاد اجزای تشكیل دهنده طرح بسیار پیچیده گشته و حجم مستندات آن خارج از كنترل میگشت. همچنین در روش سنتی طراحی از ایدههای مطرح شده در طرح هیچ گونه حفاظتی به عمل نمیآمد و امكان سواستفاده از آنها توسط اشخاصی كه طرح به آنها فروخته میشود، وجود داشت.

در طراحی یك سختافزار با توصیف متنی آن به كمك یك زبان برنامهنویسی، هم حجم مستندات طرح كاهش یافته و هم امكان حفاظت ایدههای طرح به وجود آمده است. علاوه بر این توصیف متنی یك سختافزار به كمك HDLها برای كامپیوتر قابل فهمتر از طرح شماتیكی آن سختافزار با اطلاعات تصویری میباشد. مهمترین وجه تمایز یك زبان توصیف سختافزار با یك زبان برنامهنویسی متداول مانند C ، در نحوه اجرای خطكدها میباشد، در زبانهای برنامه نویسی متداول مانند C خط كدهای نوشته شده به ترتیب از بالا به پایین اجرا شده تا در نهایت به اتمام برسند، در حالی كه در زبانهای توصیف سختافزار اجرای دستورات ماهیت ترتیبی و سریال نداشته و تمام خطكدها به صورت موازی و همزمان اجرا میشوند، در واقع برای توصیف سختافزاری كه ممكن است از چندین بخش ساخته شده باشد كه خروجی آنها به صورت همزمان تغییر میكند، زبانهای برنامهنویسی متداول با ماهیت اجرای ترتیبی خود كاربردی ندارند.

شبیه سازی سختافزار به كمك HDLها

به كمك زبانهای توصیف سختافزار علاوه بر طراحی میتوانیم یك سختافزار را شبیه سازی كرده تا قابلیتها و عملكرد آن را قبل از پیادهسازی آزمایش كنیم. در دنیای واقعی تست كردن یك سختافزار، خود نیازمند یك سختافزار دیگر است كه مجموعهای از ورودیهای مجاز را برای سختافزار زیر تست تولید كرده و خروجی حاصله را با مقدار مورد انتظار مقایسه كند. در فضای مجازی كه كامپیوتر در اختیار ما قرار داده است نیز میتوانیم قبل از پیاده سازی و ساختن سختافزار، عملكرد آنرا با طراحی یك سختافزار جانبی جهت تست، سختافزار اصلی را ارزیابی كنیم، به این ترتیب كه به كمك زبان توصیف سختافزار، برنامهای نوشته میشود تا زنجیرهای از ورودیها را به سختافزار مورد آزمایش داده و خروجی آن را با مقادیر مورد انتظار طراح مقایسه نماید، به این برنامه كه جهت آزمایش عملكرد سختافزار نوشته میشود،Testbench گفته میشود. زبانهای توصیفسختافزار Verilog و VHDL در میان سایر HDLها محبوبیت بیشتری پیدا كردهاند كه در ادامه مقاله به بررسی و مقایسهآنها خواهیم پرداخت.

زبان توصیف سختافزار VHDL :

در سال 1983 دوشركت بزرگ IBM و Texas Instrument به همراه شركت Intermetrics قراردادی را جهت توسعه این زبان برای كاربردهای طراحی مدارات دیجیتال امضا كردند و چهار سال بعد این زبان به توسط IEEE استاندارد سازی شد پس از آن وزارت دفاع آمریكا شركتهای تابع خود را مقید ساخت تا تمامی مدارات دیجیتال خود را به این زبان توصیف كنند. جگنده F-22 یكی از اولین پروژههایی بود كه تمامی مدارات و مستندات الكترونیكی آن به زبان VHDLنگاشته شده بود، موفقیت این پروژه موجب شد تا زبان VHDL بیش از پیش توسعه یافته و مورد استفاده قرار گیرد. در سال 1993 استاندارد IEEE-1076 ویرایش شد و در آن تمهیداتی جهت پوشش دادن به سیگنالهایی كه در آن واحد چند مقدار به آنها داده میشود، اندیشیده شد. در سال 1996 ابزارهای شبیه سازی و سنتز مدارات دیجیتال توصیف شده توسط VHDL به صورت تجاری عرضه شدند تا مراحل طراحی تا پیادهسازی كامپیوتری یك سختافزار به كمك VHDL تكمیل شود. در سال 2006 كمیته فنی VHDL مستقر در كنسرسیوم Accellera كه توسط IEEE جهت به روزرسانی استاندارد VHDL ایجاد شده است، نسخه سوم از پیش نویس استاندارد VHDL-2006 را ارائه كرد.

یك نمونه از برنامه VHDL كه به توصیف یك گیت AND ساده بدون ملاحظات زمانی پرداخته است در زیر آورده شده است :

-- import std_logic from the IEEE library

library IEEE;

use IEEE.std_logic_1164.all;

-- this is the entity

entity name_of_entity is

port (

IN1 : in std_logic;

IN2 : in std_logic;

OUT1: out std_logic);

end entity name_of_entity;

-- here comes the architecture

architecture name_of_architecture of name_of_entity is

-- Internal signals and components would be defined here

begin

OUT1 <= IN1 and IN2;

end architecture name_of_architecture;

زبان توصیف سختافزار Verilog :

زبان توصیف سختافزاری Verilog سرنام Verifying Logic جهت مدلسازی سیستمهای الكترونیكی ابداع شده است كه كلیه مراحل طراحی، ارزیابی و پیاده سازی یك مدار آنالوگ یا دیجیتال یا یك مدار تركیبی را در چند سطح انتزاع پوشش میدهد.Syntax این زبان بسیار مشابه به زبان C میباشد و در توسعه آن از ویژگیهای زبان C الگو گرفته شده است. این زبان در سال 1981 توسط Phil Moorby در شركت Gateway Design Automation ابداع شد و در سال 1985 نرمافزار شبیهساز این زبان به نام Verilog-XL عرضه شد در سال 1989 این شركت به همراه حقوق معنوی این زبان توسط شركت Cadance خریداری و سپس مستندات آنرا برای استفاده عمومی، به صورت رایگان در اختیار مردم قرار گرفت.در سال 1993 این زبان توسط IEEE بازنگری و استانداردسازی شد در همین سال بر اساس آمار EETimes حدود 85 درصد از طراحیهای مدارات مجتمعی كه به كارخانههای تولیدكننده ادوات نیمههادی سفارش داده شدند، به زبان Verilog توصیف شده بودند.یك نمونه از برنامه Verilog كه به توصیف یك فلیپفلاپ پرداخته است در زیر آورده شده است :

module toplevel(clock,reset);

input clock;

input reset;

reg flop1;

reg flop2;

always @ (posedge reset or posedge clock)

if (reset)

begin

flop1 <= 0;

flop2 <= 1;

end

else

begin

flop1 <= flop2;

flop2 <= flop1;

end

endmodule

از جمله امكانات زبان Verilog محیط PLI آن سر نام Program Language Interface میباشد كه به كمك آن میتوان كنترل برنامه را از زبان Verilog بر عهده تابعی كه به زبان C نوشته شده است قرار داد، این قابلیت موجب شده تا زبان Verilog انعطاف پذیر گشته و توسعه برنامه در آن توسط زبان C نیز امكان پذیر باشد.

Verilogدر برابر VHDL :

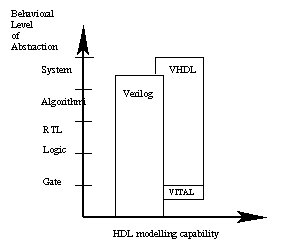

توصیف ساختاری یك سختافزار با زبان Verilog هیچ گونه برتری یا كاستی نسبت به توصیف آن با زبانVHDL ندارد و تفاوت میان این دو زبان بیشتر در توصیفهای رفتاری یك سختافزار خود را نشان میدهند. شكل زیر نشاندهنده میزان مقیاس پذیری این دو زبان در سطوح مختلف انتزاع در توصیف رفتاری میباشد:

Verilogدر برابر VHDL

همانطور كه مشاهده میكنید، زبان Verilog توانایی مدلسازی سختافزار تا پایینترین سطح انتزاع یعنی سطح ترانزیستور و سوییچ را دارا میباشد در حالی كه زبان VHDL توانایی مدلسازی سختافزار در بالاترین سطوح انتزاع (تا سطح سیستم) را دارد. علارقم اینكه به كمك قابلیت PLI زبان Verilog تا حدودی میتوان به توصیف سیستمی یك سختافزار پرداخت، اما اصولا بهرهگیری از HDL ها جهت توصیف یك سیستم ناكارآمد است و برای این منظور زبانهای كارآمد دیگری مانند SystemC و System Verilogطراحی شده كه به كمك آنها میتوان سختافزار را از بالاترین سطح انتزاع توصیف نمود. لذا قابلیتهای توصیف سیستمی VHDL را به سختی میتوان در زمره برتریهای آن نسبت به Verilog قلمداد كرد. انواع داده در زبان Verilog نسبت به VHDL ساده تر و استفاده از آنها آسانتر میباشد، ضمن اینكه این انواع داده در Verilog به مدلسازی ساختاری نزدیكتر هستند، در این زبان برخلاف VHDL انواع داده مشخصی تعریف شده است و كاربر نمیتواند انواع داده جدید به آن اضافه كند. به دلیل سادگی استفاده از انواع دادهها زبان Verilog نسبت به VHDL ارجحیت دارد. برای فردی كه پیشزمینهای در مورد زبانهای برنامه نویسی ندارد، یادگیری زبان Verilogسادهتر از VHDLاست، چرا كه نوشتن كدهای VHDL كمی پیچیده تر از Verilogمیباشد و برای تسلط بر خط كد اینVHDL، زمان بیشتری نیاز است، علاوه بر اینكه در زبان VHDL روشهای متعددی برای مدل كردن یك مدار وجود دارد كه در ساختارهای بزرگ میتواند موجب سردرگمی افراد تازه كار شود.

انتخاب یك زبان توصیف سختافزار :

برای انتخاب یك زبان جهت توصیف مدار دیجیتال، عوامل متعددی را باید علاوه بر برتریهای ذاتی یك زبان خاص مدنظر قرار داد. برخی از این عوامل عبارتند از:

- سلیقه شخصی : اصولا چون اكثر مهندسین و طراحان مدارات دیجیتال به زبان C مسلط هستند، زبانVerilog را كه خط كد مشابه C دارند ترجیح میدهند، ضمن اینكه خوانایی كدهای این زبان بهتر از VHDLاست.

- موجودیت ابزارهای شبیهسازی و سنتز : در حال حاضر ابزارهای شبیهساز رایگان متعددی برای زبانVerilog وجود دارند كه از میانآنها میتوان به كامپایلر Icarus Verilog اشاره كرد، در حالی كه ابزارهای شبیهساز متنباز اندكی برای VHDL موجود هستند و اقلب ابزارهای شبیهسازی این زبان، به صورت تجاری به فروش میرسند.

- عوامل تجاری و بازاریابی : بر اساس آمارهای منتشر شده در سال 1998بازار ابزارهای شبیهسازی زبان Verilog حدود 150 میلیون دلار اعتبار داشت به طوری كه اعتبار این بازار نسبت به سال 1994 دو برابر شده بود، در سال 2003 نیز شركت Synopses یكی از بزرگترین شركتهای این بازار چند صد میلیون دلاری، اعلام كرد كه تیم توسعه و تحقیقات این شركت تنها بر روی Verilog متمركز شده اند و در ابزارهای شبیهسازی این شركت از VHDLپشتیبانی نخواهد شد.

زبان توصیف سختافزاری Verilog مورد استقبال صنایع بزرگ قرار گرفته است به طوری كه امروزه این زبان به عنوان یك زبان پركاربرد در صنعت طراحی و تولید مدارات دیجیتال شناخته شده است. در مقابل زبانVHDL از سوی جامعه آكادمیك مورد استقبال قرار گرفته و بیشتر در پروژههای دانشگاهی از آن بهره گرفته میشود.

خودآموز زبان Verilog نگاشته جناب آقای دكتر صفری استادیار دانشگاه تهران در گروه مهندسی كامپیوتر-سختافزار:

| حداقل اشتراک | محتویات | زمان ایجاد | حجم فایل | تعداد دانلودها |

رایگان  |

جمعه, 08 دی 1391 01:21 | 708.44 KB | 1 |

تنها کاربران عضو یا دارای مجوز میتوانند دانلود نمایند |