VHDL

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 6676

واحد محاسبه و منطق (Arithmetic & Logic Unit) به اختصار (ALU)، مداری دیجیتالی است که عملیات حساب و منطق را انجام میدهد. یک قطعه اساسی از واحد پردازش مرکزی در کامپیوتر است. و حتی سادهترین میکروپردازندهها نیز دارای یک واحد محاسبه و منطق برای کارهایی از قبیل محاسبات اولیه مانند جمع و تقسیم و ... هستند. پردازندههای موجود درپردازشگر(CPU)های مدرن و و پردازندههای گرافیکی(GPU) داری واحد محاسبه و منطق قدرتمند ودر عین حال پیچیدهای هستند. ممکن است هر قطعه دارای بیش از یک واحد محاسبه و منطق باشد. جان فون نویمن که یک ریاضی دان بود مفهوم ALU را در سال 1945، هنگامی که در حال نوشتن گزارش برای کامپیوتر جدید خود به نام EDVAC بود، مطرح کرد.

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 5128

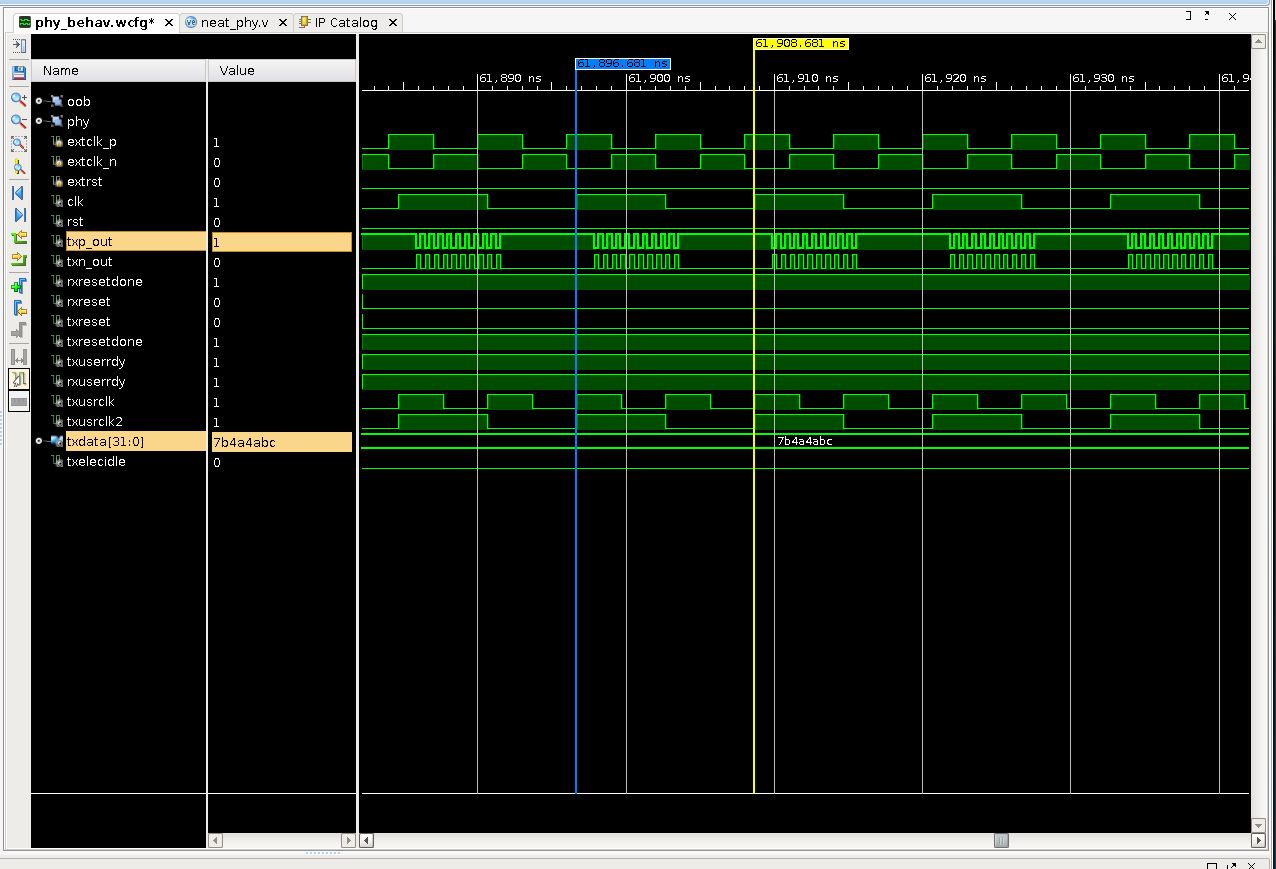

این نوع کدینگ در کنار روشهای 4b/5b و 5b/6b به روشهای کدهای بلوکی معروف هستند که بسیار که برای ارسالهای با سرعتهای بالا مورد استفاده قرار میگیرند و در واقع نگاشت بی قانون از دیتاها به دیتای متناظر برای هدفی خاص هستند.به عبارتی یک کد 8 بیتی به یک کد 10 بیتی در روش 8b/10b با هدف مساوی قرار دادن تعداد یکها وصفرها نگاشت میشود کدهای جدید میتواند برای میل به این هدف کاملا قراردادی باشد. در سال 1983 شرکت IBM یک مقاله [1] با نام A DC-Balanced, Partitioned-Block, 8b/10b Transmission Code توسط A. X. Widmer and P. A. Franaszek ارائه شد که در ابتدا برای انتقال دیتا با سرعت بالا در فیبرهای نوری مورد استفاده بود و به صورت یک اختراع به ثبت رسید.این روش کدینگ به دلیل سرعت بالا برای استفاده در ارتباط هایی که سرعت بالایی لازم دارند بسیار مفید است و در واقع برای استفاده در FPGA ها به دلیل سرعت بالای کلاک بسیار مناسب است.این روش کدینگ بر اساس ایجاد اختلاف محدود و بالانس DC است به این معنی که در هر آرایه از 20 بیت اختلاف بین تعداد یک ها و صفرها از 2 بیشتر نیست و همچنین در هر 6 بیت بیشتر از 5 صفر یا یک وجود ندارد.این دو خاصیت مزیت مهم این اختراع را مشخص میسازد چرا که اولین کاری که این روش کدینگ میکند پخش کردن یکها و صفرها در کل آرایه است تا میانگین زمان لازم برای یک ماندن و صفر ماندن بیشتر شود و با این کار زمان لازم برای شارژ و دشارژ خازنهای خط انتقال را بیشتر میکند و در نتیجه سرعت انتقال را افزایش خواهد داد و به عبارتی پهنای باند لازم برای انتقال را کاهش میدهد.این روش کدینگ در ابتدا در زمینه ی ذخیره سازی سیگنال صدا ی دیجیتال در نوارهای مغناطیسی کاربرد گسترده ای پیدا کرد.

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 8581

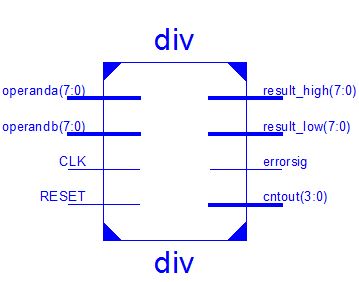

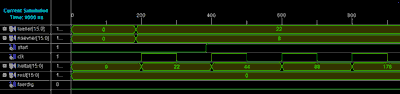

برای طراحی یک تقسیم کننده با vhdl هدف اصلی پیاده سازی به صورت کاملا ترکیبی است اما از آنجایی که پیاده سازی کاملا ترکیبی بسیار مشکل است الگوریتنهای برای تقسیم ارایه میشود که معروفترین آن تقسیم کننده ی شیفت و تفریق است.راه حل ساده تری که در ابتدا به ذهن میرسد تقیبم بر اساس یک کانتر و تفریق متوالی است که تفریق متوالی هم میتواند یک راه حل باشد ولی از آنجایی که این روش روش طولانی است به الگوریتمهای جدید تر روی می آوریم تا تعداد کلاک لازم را برای انجام یک تفریق کاهش دهیم.

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 4818

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 28966

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 13292

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 12445

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 11077

- توضیحات

- نوشته شده توسط مهدی احمدی ;-)

- دسته: VHDL

- بازدید: 18809

تمرین اول :یک برنامه برای جمع کننده ی 8 بیتی طراحی کنید. برای خروجی و ورودی از std_logic_vector نوع استفاده نمایید.