سابقه ی ARM به سال 1983 باز میگردد. هنگامی که شرکت Acron به دلیل کند بودن پردازنده های موجود در آن زمان نیاز به پردازنده ای با اجرای هر عمل در یک کلاک داشتند تا پردازنده با حافظه های سریع هماهنگ باشد,بنا بر این شرکت Acron طراحی پردازنده ی مورد نیاز خود را آغاز نمود. امروزه پردازنده های ARM هفتاد در صد پردازنده های 32 بیتی را در بر میگیرند . و عمدتا دارای ویژگی هایی از قبیل سرعت بالا ، مصرف توان کم ، قیمت پایین ، تنوع محصولات و سازگاری با محصولات قدیمی تر هستند.

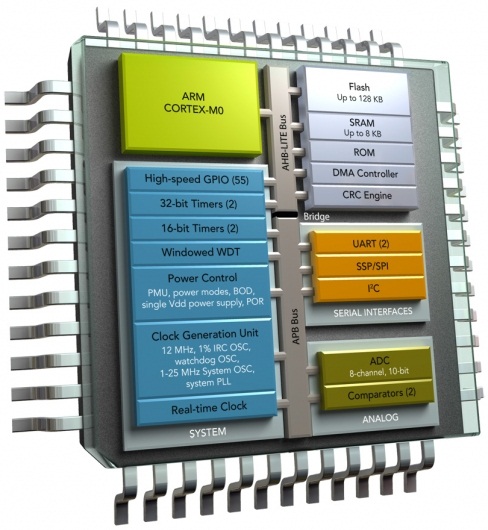

زبان برنامه نویسی پردازنده های ARM عموما C بوده و در برخی موارد برای کار با این نوع پردازنده ها از هسته های نرم افزاری Windows CE و Linux استفاده میشود. حجم کم پردازنده های ARM ، باعث شده که اکثر فضای داخلی میکروکنترلرها برای تجهیزات جانبی مانند DAC ، ADC ، USB ، LAN ، SERIAL و ... بکار گرفته شود. هسته ی تمام پردازنده های ARM کارخانجات مختلف یکی است . بنابراین برنامه ی نوشته شده برای یک سری از پردازنده ها را میتوان برای سری دیگر نیز استفاده کرد.

نسخه ی اول (ARMv1)

در سال 1985اولین پردازنده مبتنی بر معماری RISC طراحی شد.در این پردازنده کمتر از 25000 ترانزیستور به کار گرفته شده بود.این پردازنده قابلیت ضرب و کمک پردازنده را نداشت.نام ARM در واقع کوتاه شده ی (Acron RISC Machine) میباشد.

نسخه ی دوم (ARMv2)

در سال 1987 نسخه ی بعدی ARM نیز طراحی شد که قابلیت ضرب و کمک پردازنده نیز به آن اضافه شده بود.و دارای گذرگاه داده ی 32 بیتی بود و گذر گاه آدرس 26 بیتی و 16 رجیستر 32 بیتی و تنها از 30000 ترانزیستور ساخته شده بود .

نسخه ی سوم (ARMv3)

در سال 1990 شرکت Apple به ARM پیوست و شرکت Advanced RISC Machine توسط این دو تشکیل شد. این شرکت هیچ تراشه ای تولید نمیکند و تمام درامد آن حاصل از فروش حق امتیاز استفاده از هسته های ARM به شرکتهای تولید کننده ی تراشه در جهان است.

نسخه ی چهارم (ARMv4)

در سال 1996 نسخه ی چهارم ARM منتشر شد . در این نسل دستورات جابجایی داده بین رجیسترها و حافظه از نوع دو بایتی و تک بایتی به مجموعه دستورات ARM اضافه شد. در این نسخه یک مد کاری دیگر به نام system به ARM اضافه شد .بعد نسخه ی جدید ARMv4T منتشر شده که همان نسخه ی قبل بود,با این تفاوت که دستورات فشرده 16 بیتی Thumb نیز به آن اضافه شده بود.با این روش برنامه های نوشته شده با کدهای 16 بیتی نیز قابل اجرا بودند و علاوه بر آن میتوانیم برنامه ها را با کدهای 16 بیتی بنویسیم این حالت برای کاهش کد برنامه کاربرد دارد ولی از کارایی و سرکت کمتر برخوردار میباشد.

نسخه ی پنجم (ARMv5)

در سال 1999 نسخه ی پنجم با نام ARMv5T ارائه شد . که دستوراتی همچون CLZ,BKPT به مجموعه دستورات ARM و دستور BKPT به مجموعه دستورات THUMB اضافه شد و امکان بیشتری برای کمک پردازنده در نظر گرفتند.سپس در نسخه ی ARMv5TE دستور العملهایی اضافه شد برای افزایش کارایی پردازنده و پشتیبانی از پردازش سیگنال دیجیتال (DSP).در نسخه ی ARMv5TEJ با اضافه شدن دستوراتی توانایی پشتیانی از معماری Jazelle به ARM اضافه شد.

- Jazelle پیاده سازی سخت افزاری از جاوا میباشد که به پردازنده ی ARM این امکان را میدهد که بایتهای کدهای جاوا را مستقیماً اجرا نماید.

نسخه ی ششم (ARMv6)

در سال 2001 نسخه ی ششم با نام ARMv6 ارئه شد.که دستورات بسیاری به مجموعه دستورات ARM و Thumb اضافه شده بود .این نسخه از تمام ویژگیهای ARMv5TEJ پشتیبانی میکند. در این نسخه قابلیت SIMD به ARM اضافه شده است به این معنی که میتواند پردازش را به صورت 8 و 16 بیتی بر روی رجیسترها انجام دهد، زیرا برخی از برنامه ها نیازی به پردازش 32 بیتی ندارند و این باعث کاهش مصرف انرژی خواهد شد.

- رجیستر CPSR در هر نسخه بیتهای کنترلی جدیدی به آن اضافه خواهد شد.

نسخه ی هفتم (ARMv7)

در سال 2004 نسخه ی هفتم با نام های ARMv7-M , ARMv7-R , ARMv7-Aارئه شد.

- ARMv7-A : در این نسخه ی(Applications) تکنولوژی پیشرفه ی SIMD را با نام NEON به این پردازنده افزده شده است که در کاربردهایی همچون پردازش تصاویر و فشرده سازی صدا و ... به کار میرود . در این تکنولوژی 16 رجیستر 128 بیتی Q0-Q15 و 32 رجیستر 64 بیتی D0-D31 به ساختار پردازنده اضافه شد.

- ARMv7-R : در این نسخه ی (Real Time) سخت افزار تقسیم کردن به پردازنده اضافه شد.

- ARMv7-M : در این نسخه ی (Microcontroller) علاوه بر اضافه کردن سخت افزار تقسیم ، در این پردازنده فقط از دستورات Thumb وThumb-2 پشتیبانی میشود.این پردازنده فقط شامل دو مد کاری Thread Mode و Handler Mode می باشد.

- نسخه های ARMv1 و ARMv2 و ARMv3 دیگر در طراحی های امروزه استفاده ای ندارند و منسوخ شده اند.بین نسخه های یاد شده تفاوتهایی زیادی موجود میباشد که ما به برخی از آنها اشاره کردیم.

|

ARM Family |

ARM Architecture |

ARM Core |

Feature |

Cache (I/D), MMU |

|

ARM1 |

ARMv1 |

ARM1 |

First implementation |

None |

|

ARM2 |

ARMv2 |

ARM2 |

ARMv2 added the MUL (multiply) instruction |

None |

|

ARMv2a |

ARM250 |

Integrated MEMC (MMU), Graphics and IO processor. ARMv2a added the SWP and SWPB (swap) instructions. |

None, MEMC1a |

|

|

ARM3 |

ARMv2a |

ARM3 |

First integrated memory cache. |

4K unified |

|

ARM6 |

ARMv3 |

ARM60 |

ARMv3 first to support 32-bit memory address space (previously 26-bit) |

None |

|

ARM600 |

As ARM60, cache and coprocessor bus (for FPA10 floating-point unit). |

4K unified |

||

|

ARM610 |

As ARM60, cache, no coprocessor bus. |

4K unified |

||

|

ARMv3 |

ARM700 |

8 KB unified |

||

|

ARM710 |

As ARM700, no coprocessor bus. |

8 KB unified |

||

|

ARM710a |

As ARM710 |

8 KB unified |

||

|

ARMv4T |

ARM7TDMI(-S) |

3-stage pipeline, Thumb |

none |

|

|

ARM710T |

As ARM7TDMI, cache |

8 KB unified, MMU |

||

|

ARM720T |

As ARM7TDMI, cache |

8 KB unified, MMU with Fast Context Switch Extension |

||

|

ARM740T |

As ARM7TDMI, cache |

MPU |

||

|

ARM7EJ |

ARMv5TEJ |

ARM7EJ-S |

5-stage pipeline, Thumb, Jazelle DBX, Enhanced DSP instructions |

none |

|

ARM8 |

ARMv4 |

ARM810[13] |

5-stage pipeline, static branch prediction, double-bandwidth memory |

8 KB unified, MMU |

|

ARMv4 |

SA-1 |

5-stage pipeline |

16 KB/8–16 KB, MMU |

|

|

ARMv4T |

ARM9TDMI |

5-stage pipeline, Thumb |

none |

|

|

ARM920T |

As ARM9TDMI, cache |

16 KB/16 KB, MMU with FCSE (Fast Context Switch Extension)[14] |

||

|

ARM922T |

As ARM9TDMI, caches |

8 KB/8 KB, MMU |

||

|

ARM940T |

As ARM9TDMI, caches |

4 KB/4 KB, MPU |

||

|

ARMv5TE |

ARM946E-S |

Thumb, Enhanced DSP instructions, caches |

variable, tightly coupled memories, MPU |

|

|

ARM966E-S |

Thumb, Enhanced DSP instructions |

no cache, TCMs |

||

|

ARM968E-S |

As ARM966E-S |

no cache, TCMs |

||

|

ARMv5TEJ |

ARM926EJ-S |

Thumb, Jazelle DBX, Enhanced DSP instructions |

variable, TCMs, MMU |

|

|

ARMv5TE |

ARM996HS |

Clockless processor, as ARM966E-S |

no caches, TCMs, MPU |

|

|

ARM10E |

ARMv5TE |

ARM1020E |

6-stage pipeline, Thumb, Enhanced DSP instructions, (VFP) |

32 KB/32 KB, MMU |

|

ARM1022E |

As ARM1020E |

16 KB/16 KB, MMU |

||

|

ARMv5TEJ |

ARM1026EJ-S |

Thumb, Jazelle DBX, Enhanced DSP instructions, (VFP) |

variable, MMU or MPU |

|

|

ARMv5TE |

XScale |

7-stage pipeline, Thumb, Enhanced DSP instructions |

32 KB/32 KB, MMU |

|

|

Bulverde |

32 KB/32 KB, MMU |

|||

|

Monahans[15] |

Wireless MMX2 added |

32 KB/32 KB (L1), optional L2 cache up to 512 KB, MMU |

||

|

ARMv6 |

ARM1136J(F)-S[16] |

8-stage pipeline, SIMD, Thumb, Jazelle DBX, (VFP), Enhanced DSP instructions |

variable, MMU |

|

|

ARMv6T2 |

ARM1156T2(F)-S |

9-stage pipeline, SIMD, Thumb-2, (VFP), Enhanced DSP instructions |

variable, MPU |

|

|

ARMv6ZK |

ARM1176JZ(F)-S |

As ARM1136EJ(F)-S |

variable, MMU+TrustZone |

|

|

ARMv6K |

ARM11 MPCore |

As ARM1136EJ(F)-S, 1–4 core SMP |

variable, MMU |

|

|

Cortex-A |

ARMv7-A |

Cortex-A5[18] |

VFP, NEON, Jazelle RCT, Thumb/Thumb-2, 1-4 cores |

variable (L1+L2), MMU+TrustZone |

|

VFP, NEON, Jazelle RCT, Thumb-2, 13-stage superscalar pipeline |

variable (L1+L2), MMU+TrustZone |

|||

|

Application profile, VFPv3 FPU, NEON, Thumb-2, Jazelle RCT/DBX, out-of-orderspeculative issuesuperscalar, 1–4 core SMP |

32KB/32KB L1, up to 4MB L2, MMU+TrustZone |

|||

|

Application profile, VFPv4 FPU, NEON, Thumb-2, Jazelle RCT/DBX, out-of-order speculative issue superscalar, Large Physical Address Extensions (LPAE), Hardware virtualization, 1-4 SMP cores |

32KB/32KB L1, up to 4MB L2, MMU+TrustZone |

|||

|

Cortex-R |

ARMv7-R |

Cortex-R4(F) |

Real-time profile, Thumb-2, (FPU) |

variable cache, MPU optional |

|

Cortex-M |

ARMv6-M |

Cortex-M0 |

Microcontroller profile, Thumb-2 subset (16-bit Thumb instructions & BL, MRS, MSR, ISB, DSB, and DMB). Hardware multiply instruction optional |

No cache. |

|

Cortex-M1 |

FPGA targeted, Microcontroller profile, Thumb-2 subset (16-bit Thumb instructions & BL, MRS, MSR, ISB, DSB, and DMB). |

None, tightly coupled memory optional. |

||

|

ARMv7-M |

Cortex-M3 |

Microcontroller profile, Thumb-2 only. Hardware divide instruction. |

no cache, MPU optional. |

|

|

ARMv7-ME |

Cortex-M4 |

Microcontroller profile, both Thumb and Thumb-2, FPU. Hardware MAC, SIMD and divide instructions. |

MPU optional. |

بسط هاي ARM ISA

بسط هاي گوناگوني كه طي چند سال اخير همراه با معماري هاي ARM معرفي شده اند، امكانات و ويژگي هاي جديدي را به پردازنده هاي مبتني بر اين معماري افزوده اند. در ادامه به بررسي ويژگي ها و امكانات هر يك از اين بسط ها مي پردازيم.

- Thumb : مجموعه دستورالعمل هاي Thumb در نسخه چهارم معماريARM معرفي شده است كه كدهاي بيشتري را براي كاربردهاي توليدكنندگان مختلف فراهم مي كند. Thumb يك زيرمجموعه از عمومي ترين دستورالعمل هاي ARM سي و دو بيتي را كه درون كدهاي عملياتي (Opcode- كدهاي عملياتي بخشي از دستورالعمل هاي زبان ماشين هستند كه اجرا شدن عمليات را مشخص مي كند) با اندازه شانزده بيت فشرده شده است، فراهم مي كند. در زمان اجرا، اين دستورالعمل هاي شانزده بيتي مي توانند از وضعيت فشرده خارج شده و به دستورالعمل هاي ARM سي و دو بيتي مبدل شود يا به طور مستقيم توسط يك واحد رمزگشايي اختصاصي Thumb اجرا شوند. اگر چه كد Thumb نسبت به كد ARM سي و دو بيتي معادل، چهل درصد بيشتر دستورالعمل استفاده مي كند، اما به سي درصد فضاي كمتر نياز دارد. همچنين كد Thumb نسبت به كد ARM چهل درصد آهسته تر است. بنابراين Thumb موجب كاهش كارايي مي شود و به طور معمول در كارهايي كه حساس به كارايي نيستند، كاربرد دارد. Thumb اگرچه موجب كاهش كارايي مي شود، اما موجب كاهش مصرف توان سيستم مي شود كه يك معيار بسيار مناسب براي سيسستم هاي همراه به شمار مي آيد.

- Thumb 2 : يك مجموعه از دستورالعمل هاي سي و دو بيتي است كه در كنار دستورالعمل هاي شانزده بيتي سنتي كه در Thumb بكار گرفته شده بود، اجرا مي شود. Thumb 2 مي تواند نياز به Thumb را در يك سيستم كاهش داده يا به طور كامل حذف كند. اين فناوري موجب بهبود كارايي در برخي مواقع نيز موجب كاهش مصرف توان مي شود.

- Jazell : فناوري Jazell سخت افزاري است كه به پردازنده هاي ARM اجازه مي دهد تا «بايت كدهاي» جاوا را اجرا كند. آن دسته از معماري هايي كه داراي چنين ويژگي هستند، در كاربردهاي جاوا كارايي بالاتر به همراه مصرف توان پايين تر را فراهم مي كنند.

- بسط هاي DSP : سيستم هاي مبتني بر ARM وظايف پردازش سيگنال را با استفاده از كمك پردازنده DSP اختصاصي اجرا مي كنند. در برخي از مواقع پشتيباني از DSP به وسيله هسته اصلي ARM مناسب است. يك بسط ISA متناظر در پنجمين نسخه اين معماري معرفي شده است. اين ويژگي هنگامي كه عمليات جمع و تفريق و ضرب شانزده بيتي اشباع شود از آن ها پشتيباني مي كند. اين ويژگي در ششمين نسخه ARM به كار گرفته شد و به بسط مجموعه دستورالعمل هاي SIMD اضافه شد كه اجازه مي دهد دو دستورالعمل محاسباتي شانزده بيتي يا چهار دستورالعمل محاسباتي هشت بيتي به طور همزمان اجرا شود.

- NEON : اين فناوري كه گاهي با نام Advanced SIMD شناخته مي شود، در معماري نسل هفتم مورد استفاده قرار گرفته و براي كاربردهاي حرفه اي، وسايل همراه كم مصرف و علاقمندان به رسانه ها طراحي شده است. فناوري NEON يك معماري هايبريد SIMD نوع 64 يا 128 بيت است كه به وسيله ARM براي شتاب دادن به كارايي چند رسانه اي و برنامه هاي كاربردي پردازش سيگنال شامل رمزگذاري/ رمزگشايي ويدئويي، گرافيك سه بعدي، فشرده سازي رمزگشايي صوتي و پردازش تصاوير توسعه داده شده است.

ویژگی های پردازنده ی ARM

پردازنده های ARM پردازنده هایی با معماری Risk میباشند .این پردازنده ها برای کاربرد های قابل حمل بهینه سازی شده اند به صورتی که مصرف توان آنها بسیار کم بوده و میتوان آنها را توسط باتری برای مدت زیادی روشن نگه داشت . به عنوان نمونه میتوان گوشی های موبایل را نام برد که در آنها از این هسته ی پردازشی استفاده شده است. معروفترین هسته ی پردازنده ی ARM ، ARM7 میباشد. که یکی از رایج ترین هسته های پردازشی موجود میباشد. بعد از ARM7 ، به ترتیب ARM9 ، ARM10 و ARM11 میباشند که همه از معماری HARVARD استفاده میکنند.

- معروفترين هسته پردازنده ARM7 ، ARM مي باشد كه يكي از رايج ترين هسته هاي پردازشي موجود است. بعد از ARM 7 به ترتيب ARM9 و ARM10 و ARM11 قرار دارند.

انواع هسته های پردازنده ی سری ARM7

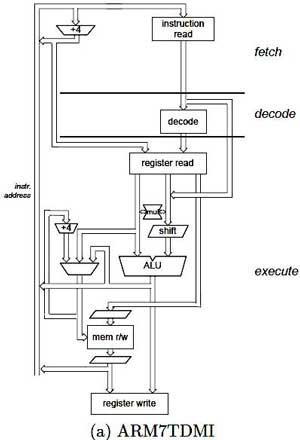

- ARM7TDMI: رایج ترین هسته ی 32 بیتی با معماری Risk می باشد.این پردازنده از معماری نسخه ی ARMv4T پشتیبانی میکند .مجهز به سه مرحله خط لوله مبتنی بر معماری Von-Neumann میباشد.توان مصرفی کم وسایز کوچک از مشخصات این پردازنده است.

- ARM7TDMI-S : این هسته نسخه ی قابل سنتز ARM7TDMI است که می توان معماری آن را توسط زبانهای توصیف سخت افزار از قبیل Verilog و VHDL پیاده سازی کرد.

- ARM72OT : این هسته علاوه بر ویژگیهای هسته های بالا دارای حافظه ی CASH و بخش مدیریت حافظه می باشد.این قابلیت پردازنده ها را قادر میسازد که توسط سیستم عاملهایی مانند Windows CE,Linux,Symbian به کار گرفته شوند.

- ARM72OT : این پردازنده از معماری نسخه ی ARMv4T پشتیبانی می کند .مجهز به سه مرحله خط لوله مبتنی بر معماری Von-Neumann میباشد . دارای 8 کیلیو باید حافظه ی نهان و بافر نوشتن و MPU میباشد.

- ARM7EJ-S : این پردازنده از معماری نسخه ی ARMv5TEJ پشتیانی میکند.مجهز به 5 مرحله خط لوله مبتنی بر معماری Von-Neumann میباشد و از تکنولوژی Jazelle و دستورات DSP پشتیبانی میکند.

انواع هسته های پردازنده ی سری ARM9

- ARM9TDMI : این پردازنده از معماری نسخه ی ARMv4T پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.

- ARM940T : این پردازنده از معماری نسخه ی ARMv4T پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 4 کیلو بایت حافظه ی نهان برای دستو العمل و 4 کیلو بایت حافظه ی نهان برای داده و دارای MPU است.

- ARM922T : این پردازنده از معماری نسخه ی ARMv4T پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 8 کیلو بایت حافظه ی نهان برای دستو العمل و 8 کیلو بایت حافظه ی نهان برای داده و دارای MMU است.

- ARM920T : این پردازنده از معماری نسخه ی ARMv4T پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 16 کیلو بایت حافظه ی نهان برای دستو العمل و16 کیلو بایت حافظه ی نهان برای داده و دارای MMU است.

- ARM9E-S : این پردازنده از معماری نسخه ی ARMv4T پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.از دستورات DSP پشتیبانی میکند.

- ARM966E-S : این پردازنده از معماری نسخه ی ARMv5TE پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.از دستورات DSP پشتیبانی میکند و دارای TCM-Tightly Coupled Memory میباشد.

- ARM968E-S : این پردازنده از معماری نسخه ی ARMv5TE پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد و دارای ITCM-Instruction TCM و DTCM - data TCM میباشد.

- ARM946E-S : این پردازنده از معماری نسخه ی ARMv5TE پشتی بانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 1000 کیلو بایت حافظه ی نهان برای دستو العمل و 1000 کیلو بایت حافظه ی نهان برای داده و دارای MPU است.

- ARM9EJ-S : این پردازنده از معماری نسخه ی ARMv5TEJ پشتیبانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.از دستورات DSP و تکنولوژی Jazelle پشتیبانی میکند.

- ARM926EJ-S : محبوب ترین پردازنده در خانواده ی ARM9 است . این پردازنده از معماری نسخه ی ARMv5TEJ پشتیبانی میکند. مجهر به 5 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 4 کیلو بایت حافظه ی نهان برای دستو العمل و 128 کیلو بایت حافظه ی نهان برای داده و دارای MMU است.از دستورات DSP و تکنولوژی Jazelle پشتیبانی میکند.

انواع هسته های پردازنده ی سری ARM10

- ARM1020E : این پردازنده از معماری نسخه ی ARMv5TE پشتیبانی میکند. مجهر به 6 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 32 کیلو بایت حافظه ی نهان برای دستو العمل و 32 کیلو بایت حافظه ی نهان برای داده و دارای MMU است.

- ARM1022E : این پردازنده از معماری نسخه ی ARMv5TE پشتیبانی میکند. مجهر به 6 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 16 کیلو بایت حافظه ی نهان برای دستو العمل و 16 کیلو بایت حافظه ی نهان برای داده و دارای MMU است.

- ARM1026EJ-S : این پردازنده از معماری نسخه ی ARMv5TEJ پشتیبانی میکند. مجهر به 6 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 128 کیلو بایت حافظه ی نهان برای دستو العمل و 128 کیلو بایت حافظه ی نهان برای داده و دارای MPU است.از دستورات DSP و تکنولوژی Jazelle پشتیبانی میکند.

انواع هسته های پردازنده ی سری ARM11

- ARM1136J-S/ARM1136FJ-S : این پردازنده از معماری نسخه ی ARMv6 پشتیبانی میکند. مجهر به 8 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 64 کیلو بایت حافظه ی نهان برای دستو العمل و 64 کیلو بایت حافظه ی نهان برای داده و دارای MMU میباشد.

- ARM1156T2-S/ARM1156T2F-S : این پردازنده از معماری نسخه ی ARMv6 پشتیبانی میکند. مجهر به 9 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 64 کیلو بایت حافظه ی نهان برای دستو العمل و 64 کیلو بایت حافظه ی نهان برای داده و دارای MMU و باس AXI-Advanced Extensible Interface میباشد.

- ARM1176JZ-S/ARM1176JZF-S : این پردازنده از معماری نسخه ی ARMv6 پشتیبانی میکند. مجهر به 8 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 64 کیلو بایت حافظه ی نهان برای دستو العمل و 64 کیلو بایت حافظه ی نهان برای داده و دارای MMU و باس AXI-Advanced Extensible Interface میباشد.

- ARM11MPCORE : این پردازنده از معماری نسخه ی ARMv6 پشتیبانی میکند. مجهر به 8 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.دارای 64 کیلو بایت حافظه ی نهان برای دستو العمل و 64 کیلو بایت حافظه ی نهان برای داده و دارای MMU و باس AXI-Advanced Extensible Interface و فاقد TCM میباشد.

انواع هسته های پردازنده ی سری CORTEX

- Cortex-M0 : این پردازنده از معماری نسخه ی ARMv6-M پشتیبانی میکند. مجهر به 3 مرحله خط لوله و مبتنی بر معماری Harvard میباشد و میتواند از Thumb-2پشتیبانی میکند.

- Cortex-M1 : این پردازنده از معماری نسخه ی ARMv6-M پشتیبانی میکند. مجهر به 3 مرحله خط لوله و مبتنی بر معماری Harvard میباشد.

- Cortex-M3 : این پردازنده از معماری نسخه ی ARMv7-M پشتیبانی میکند. مجهر به 3 مرحله خط لوله و مبتنی بر معماری Harvard میباشد. دراری MPU و سخت افزار تقسیم و امکان پیش بینی دستورات پرش را دارا میباشد.

- Cortex-A5/Cortex-A8/Cortex-A9 : این پردازنده از معماری نسخه ی ARMv7-A پشتیبانی میکند. مجهر به 13 مرحله خط لوله و مبتنی بر معماری Harvard میباشد. دراری MPU و باس AXI میباشد.دارای حافظه ی نهان سطح L1 و سطح L2 میباشد.

- Cortex-R4/Cortex-R4F : این پردازنده از معماری نسخه ی ARMv7-R پشتیبانی میکند. مجهر به 8 مرحله خط لوله و مبتنی بر معماری Harvard میباشد. دراری MPU و باس AXI میباشد.دارای حافظه ی نهان سطح L1 و سطح L2 و سخت افزار تقسیم میباشد.

سیر تکاملی خط لوله در پردازنده های ARM

استفاده از خط لوله (Pipeline) راهی برای افزایش کارایی و سرعت پردازش میباشد.در این بخش به بررسی روند تکاملی خط لوله در پردازنده های ARM می پردازیم.

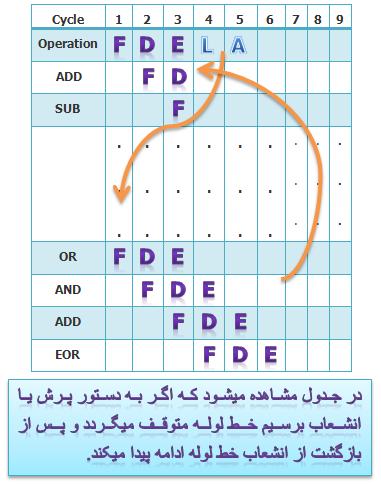

- سه مرحله خط لوله 3Stage Pipeline

سه مرحله خط لوله از نسلهای اولیه ی پردازنده های ARM تا خانواده ی ARM7 بدون تغییر بوده است. منظور از این سیستم این است که پردازنده دارای سه مد کاری برای اجرای یک دستور است:

- FETCH (واکشی) یا باز خوانی اطلاعات از حافظه ی کد

- DECODE (بازگشایی) یا رمز گشایی اطلاعات نوشته شده

- EXECUTE (اجرا) یا اجرای برنامه در پردازنده های قدیمی تر در سیکل اول دستور اول FETCH اجرا می شود ، در سیکل دوم دستور اول DECODE می شود و دستور دوم FETCH می شود . در سیکل سوم دستور اول EXECUTE دستور دوم DECODE و دستور سوم FETCH می شود ؛ این نوع سیستم 3 STAGE PIPELINE است. در پردازنده های ARM9 سیستم پردازش 5 STAGE PIPELINEمی باشدکه عملیات خواندن ونوشتن از حافظه ها نیز جزء این عملیات قرار گرفته در ARM10 سیستم پردازش به صورت 6 STAGE PIPELINE است.

- حال اگر در دستورات به انشعاب یا پرش برسد این دسورات باعث متوقف شدن روند خط لوله و اجرای مجدد آن میشوند.

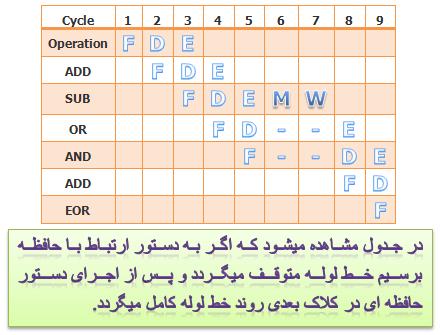

- اگر در اجرای دستورات با دستوری که با حافظه ی داده در ارتباط است برسد چون در Arm7 از آرایش Von-neuman استفاده میگردد و گذر گاه داده و آدرس مشترک میباشند در اجرای این دستور نمیتوان عمل واکشی دستورات بعد را انجام داد پس در اینجا تا تمام شدن اجرای دستور روند خط لوله متوقف میگردد.

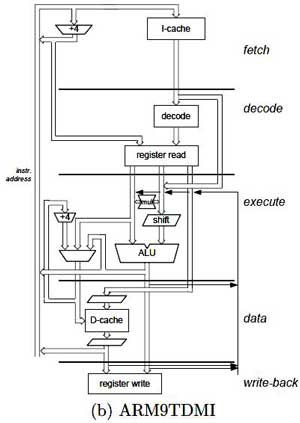

- پنج مرحله خط لوله 5Stage Pipeline

پنج مرحله خط لوله در خانواده ی ARM9 با معماری Harvard که دارای گذرگاه داده و آدرس مجزاست استفاده میشود.در این روش دستورات طی 5 مرحله ی زیر پردازش میشوند:

- FETCH (واکشی) یا باز خوانی اطلاعات از حافظه ی کد

- DECODE (بازگشایی) یا رمز گشایی اطلاعات نوشته شده

- EXECUTE (اجرا) پردازش دستورهایی که با ALU و واحد Shift رابطه دارد.

- Memory (حافظه) دسترسی به حافظه ی داده در صورت نیاز

- Write (نوشتن) نتایج محاسبات و یا داده ها از حافظه در رجیسترها نوشته میشود

- در شکل پنج مرحله خط لوله در ARM9 را مشاهده میکنید.دستورات پرش و انشعاب باعث توقف روند خط لوله و اجرای مجدد آن میشوند.

- شش مرحله خط لوله 6Stage Pipeline

شش مرحله خط لوله در خانواده ی ARM10 با معماری Harvard استفاده میشود....

....

- هشت مرحله خط لوله 8Stage Pipeline

هشت مرحله خط لوله در خانواده ی ARM11 با معماری Harvard استفاده میشود.....

....

ویژگی های انواع میکروکنترلر های ARM

میکروکنترلر های ARM دارای اجزای مختلفی از قبیل ETHERNET ، ADC ، USB و ... می باشند .که استفاده از مدارات جانبی را به حد زیاد کاهش داده است. میکروکنترلر های با هسته ی ARM7 ، برای کارهای کنترلی ساده تر در نظر گرفته شده و میکروکنترلرهایی که با هسته ی ARM9 می باشند ، اغلب در مواردی استفاده می شوند که در آنها سیستم عامل به کار برده می شود این میکروکنترلر ها سرعت بالاتری نسبت به میکروکنترلرهای با هسته ی ARM7 دارند .

کامپايلر ها و مفسر هاي موجود براي چيپ هاي ARM

- IAR: قابليت برنامه نويسي ميکرو کنترل هاي ارم ببه زبان هاي C و C++و اسمبلي ، امکان شبيه سازي برنامه نوشته شده ، پشتيباني تمامي ميکروکنترلر هاي ارم ، منابع اموزشي متوسط و محيط حرفه اي ، پشتيباني از SPY-C که امکانات خيلي زيادي دارد ، سرعت اجراي بالا و سازگاري کامل با ANSI C ، توابع کتاب خانه اي کم ، نداشتن باگ هاي امنيتي.

- Winarm : قابليت برنامه نويسي به زبان هاي C و C++ ، عدم شبيه سازي برنامه ، فقط پشتيباني ARM7 ، منابع آموزشي و مثال هاي زياد ، متن باز بودن برنامه و بالطبع رايگان بودن ، داشتن توابع کتابخانه اي بالا ، 3 سال است که اين نرم افزار به روز رساني نشده است.

- Keil : برنامه نويسي به زبان هاي Cو C++واسمبلي ، امکان شبيه سازي برنامه نوشته شده ، پشتيباني تمام ميکروکنترلر هاي ARM ، کاربرپسند بودن برنامه و منابع اموزشي متوسط

- ساير کامپايلر ها : Cross works for ARM , Flowcode ARM, ARM ADS,تقريبا دو کامپايلر keil و IAR از محبوبيت بيشتري برخوردارند.

انتخاب میکرو کنترلر

شرکت های مختلفی میکروکنترلر های بر مبنای پروسسور ARM می سازند مانند : atmel , Philips ,Samsung , St-micro , Motorola و کمپانی های دیگر حال به مقایسه ی میکرو کنترلرهای LPC شرکت Philips و AT91SAMاز شرکت atmel میپردازیم :

- قطعات سری LPC2000 یکی از متنوعترین خانواده های میکروکنترلرهای با هستهی ARM7 هستند و قطعات این سری، در مقایسه با AT91SAM قیمت کمتری دارند. مثلاً قیمت LPC2101 حدود 2 دلار است که این مقدار از خیلی از میکروکنترلرهای 8 بیتی (مثل ATmega16) کمتر است.

- اجرای برنامه از حافظ هی فلش بسیار سریعتر است. بدلیل دسترسی 128 بیتی به حافظهی فلش و وجود واحد شتابدهندهی حافظه (MAM)، قطعات LPC2000 میتوانند در مُد ARM با حداکثر سرعت 60 تا 75 MHz به حافظهی فلش دسترسی داشته باشند؛ در حالیکه که SAM7ها با سرعتی کمتر از نصف این مقدار کد برنامه را اجرا میکنند. علاوه براین، در مقایسه با سایر میکروهای با هسته ی ARM7، فرکانس کاری میکروکنترلرهای LPC2000 نسبتاً بالاست (60 تا 70 مگاهرتز در LPC2000ها در مقایسه با 55 مگاهرتر در sam

- راهاندازی Peripheralهای قطعات LPC2000 سادهتره. اکثر سختافزارهای جنبی به شکلی طراحی شدهاند که لازمه رجیسترهای کمتری تنظیم بشن و بسیاری از اونها را میتونید به حالت پیشفرض رها کنید.

- میکروکنترلرهای LPC2000 دارای Peripheralهایی هستند که به ندرت در سایر میکروکنترلرهای با هستهی ARM7 دیده میشه. مثلاً تایمر 32 بیتی با پیشتقسیمکنندهی 32 بیتی (AT91SAMها فقط تایمر 16 بیتی دارن!)، DAC، RTC، LIN، SSP، MMC/SD Controller، USB Host/OTG، Fast GPIO ،XGA LCD Controller و غیره.

- قطعات LPC دارای تعداد I/O بیشتری هستند. مثلاً قطعهی LPC2132 که یک قطعهی 64 پایه است 47 پایهی GPIO داره درحالیکه قطعه ی مشابه 64 پایه ای AT91SAM7S64، دارای 32 خط I/O است. مستندات و نمونه برنامه های ارائه شده توسط NXP برای LPCها کاملتر و غنی از ATmel برای SAM7هاست.

پردازنده هاي Atom سري Z

اينتل اين سري از پردازنده ها را براي رقابت با پردازنده هاي ARM عرضه كرده است. پردازنده هاي مبتني بر معماري ARM به دليل مصرف توان پايين محبوبيت فوق العاده اي پيدا كرده اند و بيشتر سازندگان از آن ها در تلفن ها، PDAها و GPS استفاده كرده اند. پردازنده هاي اتم سري Z از دستورالعمل هاي SIMD (از MMX گرفته تاSSSE3)، EIST (Enhanced Intel SpeedStep Technology) و Hyper Threading پشتيباني مي كنند. گذرگاه FSB به صورت QDR عمل مي كند و داراي فركانس هاي 400 و 533 مگاهرتز است. اينتل به جاي استفاده از پل شمالي و جنوبي از يك چيپ ست براي كنترل اين سري از پردازنده ها استفاده كرده و آن را SCH (System Controller Hub) ناميده است. SCH شامل يك درگاه PATA (Ultra DMA 5,100 MB/s)، واحد پردازش صداي HD دوكاناله، پشتيباني از دو مسير PCI-Express (براي كارت هاي Wi-Fiو ...) و هشت پورت USB است. SCH داراي گرافيك مجتمع بوده و از حافظه DDR2 با ولتاژ 5/1 ولت پشتيباني مي كند (برخلاف JEDEC كه براي DDR2 ولتاژ 8/1 ولت قرار داده است). پردازنده گرافيكي به كار گرفته شده در SCH هسته GMA 500 است كه از فناوري سايه زني نسخه 3+ پشتيباني مي كند. نكته قابل توجه در مورد GMA 500 پشتيباني از رمزگشايي سخت افزاري و فرمت هاي H.264، VC1، MPEG4، MPEG2 و WMV9 است. فركانس اين واحد پردازش گرافيكي صد يا دويست مگاهرتز بستگي به نوع چيپ ست آن دارد. توان مصرفي SCH تقريباً 3/2 وات است. به طور كلي، SCH همراه با پردازنده اتم سري Z تواني كمتر از پنج وات را مصرف مي كند.